Hi there, I'm Niansong Zhang

Currently, I'm working on a few interesting projects with the following labs:

I was an intern at NOVAUTO Technology.

I worked at Intel Labs on Domain-Specific Language for Agile Design from Feburary to August 2021.

What I'm working on

What I'm working on

I want to make hardware designing and implementation faster and easier.

- FPGA Compiler

I worked on an automatic hard block placer RapidLayout with Prof. Nachiket Kapre at the University of Waterloo. We want to make placement for large-scale accelerators faster and easier. This project is still active as we work to bring RapidLayout more general.

- Deep Learning Tool Chain

At NICS lab and Novauto Technology, I worked on deploying neural networks on FPGAs. Specifically, this process includes network pruning, quantization and compilation. I maintain a set of tools to deploy TensorFlow, PyTorch and Caffe neural network models on Xilinx FPGA.

- Domain-Specific Languages

I am in the developer team of HeteroCL, a next-generation heterogenous DSL. HeteroCL decouples key hardware customizations from the algorithm specification, which boosts hardware developing efficiency and design portability. I developed a SystemC backend to generate ASIC design at Intel. Currently, there are many exciting projects going on around HeteroCL, including efforts for hardware verification, sparse architectures, and MLIR integration.

My Blog

My Blog

I maintain a personal blog website: zzzdavid.tech. Just trying to put down things I'm doing and stuff that I read or learned.

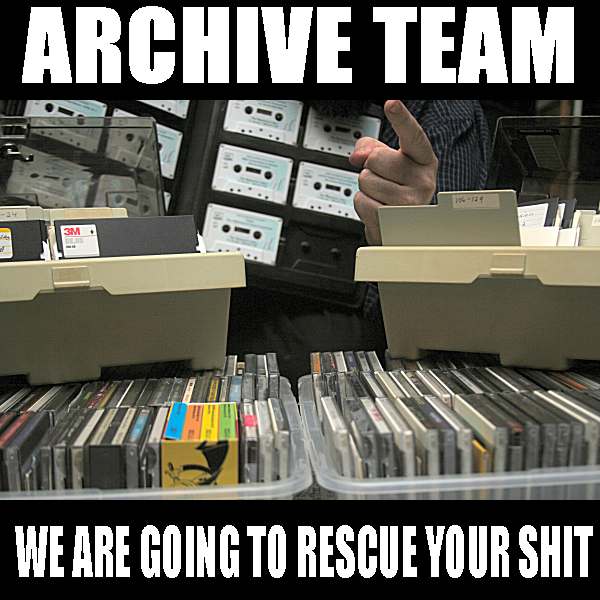

Formed in 2009, the Archive Team (not to be confused with the archive.org Archive-It Team) is a rogue archivist collective dedicated to saving copies of rapidly dying or deleted websites for the sake of history and digital heritage. The group is 100% composed of volunteers and interested parties, and has expanded into a large amount of related projects for saving online and digital history.

Formed in 2009, the Archive Team (not to be confused with the archive.org Archive-It Team) is a rogue archivist collective dedicated to saving copies of rapidly dying or deleted websites for the sake of history and digital heritage. The group is 100% composed of volunteers and interested parties, and has expanded into a large amount of related projects for saving online and digital history.